首页>66AK2G12ABYA100>规格书详情

66AK2G12ABYA100集成电路(IC)的DSP(数字信号处理器)规格书PDF中文资料

| 厂商型号 |

66AK2G12ABYA100 |

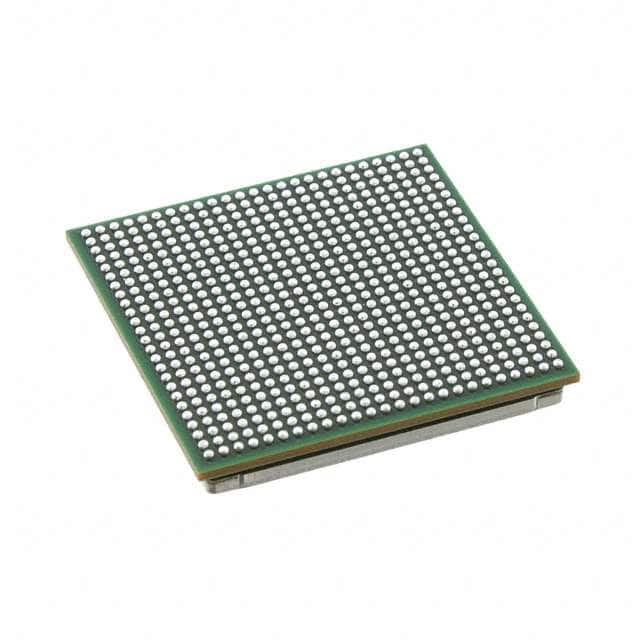

| 参数属性 | 66AK2G12ABYA100 封装/外壳为625-LFBGA,FCBGA;包装为托盘;类别为集成电路(IC)的DSP(数字信号处理器);产品描述:DSP/DSC |

| 功能描述 | 66AK2G1x Multicore DSPArm KeyStone II System-on-Chip (SoC) |

| 丝印标识 | |

| 封装外壳 | FCCSP / 625-LFBGA,FCBGA |

| 文件大小 |

2.59442 Mbytes |

| 页面数量 |

233 页 |

| 生产厂商 | Texas Instruments |

| 企业简称 |

TI2【德州仪器】 |

| 中文名称 | 美国德州仪器公司官网 |

| 原厂标识 | TI2 |

| 数据手册 | |

| 更新时间 | 2025-8-2 8:14:00 |

| 人工找货 | 66AK2G12ABYA100价格和库存,欢迎联系客服免费人工找货 |

66AK2G12ABYA100规格书详情

66AK2G12ABYA100属于集成电路(IC)的DSP(数字信号处理器)。由美国德州仪器公司制造生产的66AK2G12ABYA100DSP(数字信号处理器)数字信号处理器是类似于微处理器或微控制器的器件,但区别在于其内部架构经修改,适用于对连续数据流连续执行以乘法和加法运算为主的算法,而不是以条件逻辑或大量并发进程为主的算法。该器件通常用于诸如音频或视频信号处理等应用。

1.1 Features

1Processor cores:

• Arm® Cortex®-A15 microprocessor unit (Arm A15)

subsystem at up to 1000 MHz

– Supports full Implementation of Armv7-A

architecture instruction set

– Integrated SIMDv2 ( Arm® Neon™ Technology)

and VFPv4 (Vector Floating Point)

– 32KB of L1 program memory

– 32KB of L1 data memory

– 512KB of L2 memory

– Error Correction Code (ECC) protection for L1

data memory ECC for L2 memory

– Parity protection for L1 program memory

– Global Timebase Counter (GTC)

– 64-Bit free-running counter that provides

timebase for Arm A15 internal timers

– Compliant to Armv7 MPCore Architecture for

Generic Timers

• C66x fixed- and floating-point VLIW DSP

subsystem at up to 1000 MHz

– Fully object-code compatible With C67x+ and

C64x+ cores

– 32KB of L1 program memory

– 32KB of L1 data memory

– 1024KB of L2 configurable as L2 RAM or cache

– Error detection for L1 program memory

– ECC for L1 data memory

– ECC for L2 data memory

Industrial subsystem:

• Up to Two Programmable Real-Time Unit and

Industrial Communication Subsystems (PRUICSS),

each supports:

– Two Programmable Real-Time Units (PRUs)

with enhanced multiplier and accumulator, each

PRU supports:

– 16KB of program memory With ECC

– 8KB of data memory With ECC

– CRC32 and CRC16 hardware accelerator

– 20 × enhanced GPIO

– Serial Capture Unit (SCU), supporting direct

connection, 16-bit parallel capture, 28-bit

shift, MII_RT, EnDat 2.2 protocol and Sigma-

Delta demodulation

– Scratch pad and XFR direct connect

– 64KB of general-purpose memory With ECC

– One Ethernet MII_RT module with two MII ports

configurable for connection with each PRU;

supports multiple industrial communication

protocols

– Industrial Ethernet Peripheral (IEP) to manage

and generate industrial Ethernet functions

– Built-In Universal Asynchronous Receiver and

Transmitter (UART) 16550, with a dedicated

192-MHz clock to support 12-Mbps PROFIBUS®

– Built-In industrial Ethernet 64-Bit timer

– Built-In enhanced capture module (eCAP)

Memory subsystem:

Multicore Shared Memory Controller (MSMC) with

1024KB of shared L2 RAM

– Provides high-performance interconnect to

internal shared SRAM and DDR EMIF for both

Arm A15 and C66x Access

– Supports Arm I/O coherency where Arm A15 is

cache coherent to other system masters

accessing the MSMC-SRAM or DDR EMIF

– Supports ECC on SRAM

Up to 36-Bit DDR External Memory Interface

(EMIF)

– Supports DDR3L at up to 1066 MT/s

– Supports 4-GB memory address range

– Supports 32-Bit SDRAM data bus with 4-bit

ECC

– Supports 16-Bit and 32-Bit SDRAM data bus

without ECC

General-Purpose Memory Controller (GPMC)

– Flexible 8- and 16-Bit asynchronous memory

interface with up to four chip selects

– Supports NOR, Muxed-NOR, SRAM

– Supports general-purpose memory-port

expansion with the following modes:

– Asynchronous read and write access

– Asynchronous read page access (4-, 8-, 16-

Word16)

– Synchronous read and write access

– Synchronous read burst access without wrap

capability (4-, 8-, 16-Word16)

Network Subsystem (NSS):

Ethernet MAC (EMAC) subsystem

– One-port Gigabit Ethernet: RMII, MII, RGMII

– Supports 10-, 100-, 1000-Mbps full duplex

– Supports 10-, 100-Mbps half duplex

– Supports Ethernet Audio Video Bridging (eAVB)

– Maximum frame size 2016 Bytes (2020 Bytes

with VLAN)

– Eight priority level QOS support (802.1p)

– IEEE 1588v2 (2008 Annex D, Annex E, and

Annex F) to facilitate Audio Video Bridging

802.1AS Precision Time Protocol (PTP)

– CPTS module with timestamping support for

IEEE 1588v2

– DSCP priority mapping (IPv4 and IPv6)

– MDIO module for PHY management

– Enhanced statistics collection

• Navigator Subsystem (NAVSS)

– Built-In packet DMA controller for optimized

network processing

– Built-In Queue Manager (QM) for optimized

network processing

– Supports up to 128 queues

– 2048 buffers supported in internal queue

RAM

• Crypto Engine (SA) supports:

– Crypto Function Library for AES, DES, 3DES,

SHA1, MD5, SHA2-224 and SHA2-256

Operations

– Block data encryption supported through

hardware cores

– AES with 128-, 192-, and 256-Bit Key

supports

– DES and 3DES with 1, 2, or 3 Different Key

support

– Programmable Mode Control Engine (MCE)

– Public Key Accelerator (PKA) with elliptic curve

cryptography

– Elliptic Curve Diffie–Hellman (ECDH) based key

exchange and digital signature (ECDSA)

applications

– Authentication for SHA1, MD5, SHA2-224 and

SHA2-256

– Keyed HMAC operation through hardware core

– True Random Number Generator (TRNG)

Display Subsystem:

• Supports one video pipe with in-loop scaling, color

space

• Conversion and background color overlay

• Input data format: BITMAP, RGB16, RGB24,

RGB32, ARGB16, ARGB32, YUV420, YUV422,

and RGB565-A8

• Supported display interfaces:

– MIPI® DPI 2.0 parallel interface

– RFBI (MIPI-DBI 2.0) up to QVGA at 30fps

– BT.656 4:2:2

– BT.1120 4:2:2 up to 1920 × 1080 at 30fps

• In-loop scaling capability

• LCD interface supports:

– Active Matrix (TFT)

– Passive Matrix (STN)

– Grayscale

– TDM

– AC Bias Control

– Dither

– CPR

Asynchronous Audio Sample Rate Converter

(ASRC)

• High performance asynchronous sample rate

converter with 140 dB Signal-to-Noise (SNR)

• Up to 8 stereo streams (16 audio channels)

• Automatically sensing / detection of input sample

frequencies

• Attenuation of sampling clock jitter

• 16-, 18-, 20-, 24-Bit data input/output

• Audio sample rates from 8 kHz to 216 kHz

• Input/output sampling ratios from 16:1 to 1:16

• Group mode, where multiple ASRC blocks use the

same timing loop for input or output

• Linear phase FIR filter

• Controllable soft mute

• Independent clock generator, and rate and stamp

generator, for each input and output clock zone

• Separate DMA events for input and output, for

each channel and group

High-speed serial interfaces:

• PCI Express® 2.0 port with integrated PHY:

– Single lane Gen2-compliant port

– Root Complex (RC) and End Point (EP) modes

• Up to two USB 2.0 High-Speed dual-role ports with

Integrated PHYs, support:

– Dual-role-device (DRD) Capability with:

– USB 2.0 peripheral (or device) at

HS (480Mbps) and FS (12Mbps) speeds

– USB 2.0 host at HS (480Mbps),

FS (12Mbps), and LS (1.5Mbps) speeds

– USB 2.0 static peripheral and static host

operations

– xHCI controller with the following features:

– Compatible to the xHCI specification (revision

1.1) in host mode

– All modes of transfer (control, bulk, interrupt,

and isochronous)

– 15 transmit (TX), 15 receive (RX) endpoints

(EPs), and one bidirectional endpoint (EP0)

Flash media interfaces:

• QSPI™ with XIP and up to four chip selects,

supports:

– Memory-mapped direct mode of operation for

performing FLASH data transfers and executing

code from FLASH memory (XIP)

– Supports up to 96 MHz

– Internal SRAM buffer with ECC

– High speed read data capture mechanism

• Two Multimedia Card (MMC) and Secure Digital

(SD) ports

– Supports JEDEC JESD84 v4.5-A441 and SD3.0

physical layer with SDA3.00 standards

– MMC0 supports 3.3-V I/O for:

– SD DS and HS mode

– eMMC mode HS-SDR

up to 48 MHz

– MMC1 supports 1.8-V I/O modes for eMMC,

including HS-SDR and DDR at up to 48 MHz

with 4- and 8-Bit bus width

Audio peripherals:

• Three Multichannel Audio Serial Port (McASP)

peripherals

– Transmit and receive clocks up to 50 MHz

– Two independent clock zones and independent

transmit and receive clocks per McASP

– Up to 16-, 10-, 6-serial data pins for McASP0,

McASP1, and McASP2, respectively

– Supports TDM, I2S, and similar formats

– Supports DIT mode

– Built-In FIFO buffers for optimized system traffic

• Multichannel Buffered Serial Port (McBSP)

– Transmit and receive clocks up to 50 MHz

– Two clock zones and two serial-data pins

– Supports TDM, I2S, and similar formats

Real-time control interfaces:

• Six Enhanced High Resolution Pulse Width

Modulation (eHRPWM) Modules, Each Counter

supports:

– Dedicated 16-Bit Time-Base with Period and

Frequency Control

– Two independent PWM outputs with single edge

operation

– Two independent PWM outputs with dual-edge

symmetric operation

– One independent PWM output with dual-edge

asymmetric operation

• Two 32-Bit Enhanced Capture Modules (eCAP):

– Supports one capture input or one auxiliary

PWM output configuration options

– 4-Event time-stamp registers (Each 32-Bits)

– Interrupt on either of the four events

• Three 32-Bit Enhanced Quadrature Pulse Encoder

Modules (eQEP), each supports:

– Quadrature decoding

– Position counter and control unit for position

measurement

– Unit time base for speed and frequency

measurement

General connectivity:

• Two Controller Area Network (CAN) Ports

– Supports CAN v2.0 Part A, B (ISO 11898-1)

protocol

– Bit rates up to 1 Mbps

– Dual clock source

– ECC protection for message RAM

• One Media Local Bus (MLB)

– Supports both 3-pin (up to MOST50, 1024 × Fs)

and 6-pin (up to MOST150, 2048 × Fs) versions

of MediaLB® Physical layer specification v4.2

– Supports all types of data transfer over 64

logical channels (synchronous stream,

isochronous, asynchronous packet, control

message)

– Supports 3-wire MOST 150 protocol

• Three Inter-Integrated Circuit (I2C) interfaces, each

supports:

– Standard (up to 100 kHz) and

Fast (up to 400 kHz) modes

– 7-Bit addressing mode

– Supports EEPROM size up to 4Mbit

• Four Serial Peripheral Interfaces (SPI), each

supports:

– Operates at up to 50 MHz in master mode and

25 MHz in slave mode

– Two chip selects

• Three UART interfaces

– All UARTs are 16C750-compatible and operate

at up to 3M baud

– UART0 supports 8 pins with full modem control,

with DSR, DTR, DCD, and RI signals

– UART1 and UART2 are 4-pin interfaces

• General-Purpose I/O (GPIO)

– Up to 212 GPIOs muxed with other interfaces

– Can be configured as interrupt pins

Timers and miscellaneous modules:

• Seven 64-Bit timers:

– Two 64-Bit timers dedicated to Arm A15 and

DSP cores (one timer per core)

– Watchdog and General-Purpose (GP)

– Four 64-Bit timers are shared for general

purposes

– Each 64-Bit timer can be configured as two

individual 32-Bit timers

– One 64-Bit timer dedicated for PMMC

– Two timers input/output pin pairs

• Interprocessor communication with:

– Message manager to facilitate multiprocessor

access to the PMMC:

– Provides hardware acceleration for pushing

and popping messages to/from logical

queues

– Supports up to 64 queues and 128 messages

– Semaphore module with up to 64 independent

semaphores and 16 masters (device cores)

• EDMA with 128 (2 × 64) channels and

1024 (2 × 512) PaRAM entries

Keystone II System on Chip (SoC)

architecture:

• Security

– Supports General-Purpose (GP) and High-

Secure (HS) devices

– Supports secure boot

– Supports customer secondary keys

– 4KB of One-Time Programmable (OTP) ROM

for customer keys

• Power management

– Integrated Power Management Microcontroller

(PMMC) technology

• Supports primary boot from UART, I2C, SPI,

GPMC, SD or eMMC, USB device firmware

upgrade v1.1, PCIe®, and Ethernet interfaces

• Keystone II debug architecture with integrated Arm

CoreSight™ support and trace capability

Operating Temperature (TJ):

• –40°C to 125°C (Industrial Extended)

• –40°C to 105°C (Extended)

• 0°C to 90°C (Commercial)

1.2 Applications

• Industrial Communications and Controls

• Home Audio

• Professional Audio

• Protection Relays

• Industrial Transport

1.3 Description

66AK2G1x is a family of heterogeneous multicore System-on-Chip (SoC) devices based on TI’s fieldproven

Keystone II (KS2) architecture. These devices address applications that require both DSP and Arm

performance, with integration of high-speed peripheral and memory interfaces, hardware acceleration for

network and cryptography functions, and high-level operating systems (HLOS) support.

Similar to existing KS2-based SoC devices, the 66AK2G1x enables both the DSP and Arm cores to

master all memory and peripherals in the system. This architecture facilitates maximum software flexibility

where either DSP- or Arm-centric system designs can be achieved.

The 66AK2G1x significantly improves device reliability by extensively implementing error correction code

(ECC) in processor cores, shared memory, embedded memory in modules, and external memory

interfaces. Full analysis of soft error rate (SER) and power-on-hours (POH) shows that the designated

66AK2G1x parts satisfy a wide range of industrial requirements.

Accompanied by the new Processor SDK, the 66AK2G1x development platform enables unprecedented

ease-of-use with main line open source Linux, Code Composer Studio™ (CCS) - Integrated Development

Environment (IDE), a wide range of OS-independent device drivers, as well as TI-RTOS that enables

seamless task management across processor cores. The device also features advanced debug and trace

technology with the latest innovations from TI and Arm, such as system trace and seamless integration of

the Arm CoreSight components.

Secure boot can also be made available for anticloning and illegal software update protection. For more

information about secure boot, contact your TI sales representative.

产品属性

更多- 产品编号:

66AK2G12ABYA100

- 制造商:

Texas Instruments

- 类别:

集成电路(IC) > DSP(数字信号处理器)

- 系列:

66AK2G1x KeyStone II Multicore

- 包装:

托盘

- 类型:

DSP+ARM®

- 接口:

CAN,DMA,EBI/EMI,以太网,I²C,McASP,McBSP,MMC/SD,QSPI,SPI,UART,USB

- 时钟速率:

1GHz

- 非易失性存储器:

外部

- 片载 RAM:

1MB

- 电压 - I/O:

1.8V,3.3V

- 电压 - 内核:

1.00V

- 工作温度:

-40°C ~ 105°C(TJ)

- 安装类型:

表面贴装型

- 封装/外壳:

625-LFBGA,FCBGA

- 供应商器件封装:

625-FCBGA(21x21)

- 描述:

DSP/DSC

| 供应商 | 型号 | 品牌 | 批号 | 封装 | 库存 | 备注 | 价格 |

|---|---|---|---|---|---|---|---|

TI(德州仪器) |

24+ |

FCBGA625 |

7350 |

现货供应,当天可交货!免费送样,原厂技术支持!!! |

询价 | ||

TI(德州仪器) |

2024+ |

FCBGA-625 |

500000 |

诚信服务,绝对原装原盘 |

询价 | ||

Texas |

25+ |

25000 |

原厂原包 深圳现货 主打品牌 假一赔百 可开票! |

询价 | |||

TI |

22+ |

625-FCBGA(21x21) |

5000 |

全新原装,力挺实单 |

询价 | ||

TI |

23+ |

625-FCBGA21x21 |

8300 |

原装现货 |

询价 | ||

TEXAS INSTRUMENTS |

2022+ |

原厂原包装 |

8600 |

全新原装 支持表配单 中国著名电子元器件独立分销 |

询价 | ||

TI(德州仪器) |

2447 |

FCBGA-625(21x21) |

31500 |

60个/袋一级代理专营品牌!原装正品,优势现货,长期 |

询价 | ||

Texas Instruments(德州仪器) |

22+ |

NA |

500000 |

万三科技,秉承原装,购芯无忧 |

询价 | ||

Texas Instruments |

25+ |

625-LFBGA FCBGA |

9350 |

独立分销商 公司只做原装 诚心经营 免费试样正品保证 |

询价 | ||

Texas Instruments |

20+ |

FCBGA-625 |

15988 |

TI全新DSP-可开原型号增税票 |

询价 |