A6810SA集成电路(IC)配电开关负载驱动器规格书PDF中文资料

| 厂商型号 |

A6810SA |

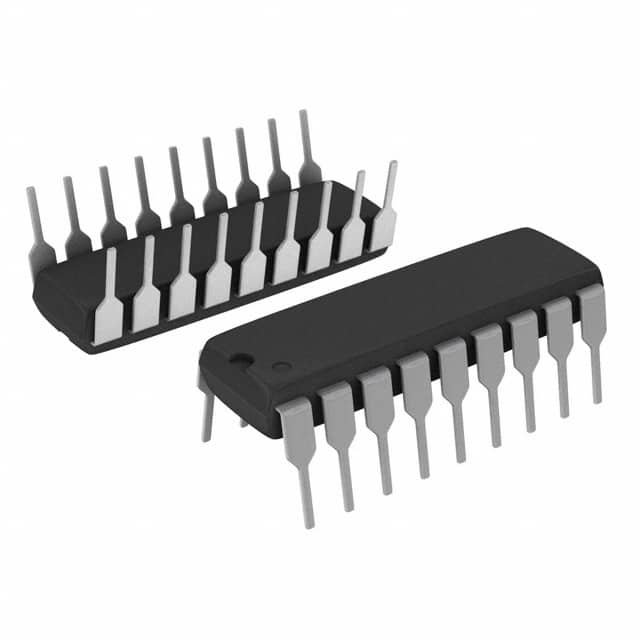

| 参数属性 | A6810SA 封装/外壳为18-DIP(0.300",7.62mm);包装为卷带(TR);类别为集成电路(IC) > 配电开关,负载驱动器;产品描述:IC PWR DRVR BIPOLAR 1:10 18DIP |

| 功能描述 | DABiC-IV, 10-BIT SERIAL-INPUT, LATCHED SOURCE DRIVERS |

| 文件大小 |

150.16 Kbytes |

| 页面数量 |

8 页 |

| 生产厂商 | Allegro MicroSystems |

| 企业简称 |

Allegro |

| 中文名称 | Allegro MicroSystems官网 |

| 原厂标识 |  |

| 数据手册 | |

| 更新时间 | 2024-4-29 19:20:00 |

A6810SA规格书详情

The A6809– and A6810– devices combine 10-bit CMOS shift registers, accompanying data latches and control circuitry with bipolar sourcing outputs and pnp active pull downs. Designed primarily to drive vacuum-fluorescent displays, the 60 V and -40 mA output ratings also allow these devices to be used in many other peripheral power driver applications. The A6809– and A6810– feature an increased data input rate (compared with the older UCN/UCQ5810-F) and a controlled output slew rate. The A6809xLW and A6810xLW are identical except for pinout.

The CMOS shift register and latches allow direct interfacing with microprocessor-based systems. With a 3.3 V or 5 V logic supply, typical serial-data input rates are up to 33 MHz.

A CMOS serial data output permits cascade connections in applications requiring additional drive lines. Similar devices are avail-able as the A6811– (12 bits), A6812– (20 bits), and A6818– (32 bits). The A6809– and A6810– output source drivers are npn Darling tons, capable of sourcing up to 40 mA. The controlled output slew rate reduces electromagnetic noise, which is an important consideration in systems that include telecommunications and/or microprocessors and to meet government emissions regulations. For inter-digit blanking, all output drivers can be disabled and all sink drivers turned on with a BLANKING input high. The pnp active pull-downs will sink at least 2.5 mA.

All devices are available in two temperature ranges for optimum performance in commercial (suffix S-) or industrial (suffix E-) applications. The A6810– is provided in three package styles for through-hole DIP (suffix -A), surface-mount SOIC (suffix -LW), or minimum-area surface-mount PLCC (suffix -EP). The A6809– is provided in the SOIC (suffix -LW) only. Copper lead frames, low logic-power dissipation, and low output-saturation voltages allow all devices to source 25 mA from all outputs continuously over the maximum operating temperature range.

FEATURES

■ Controlled Output Slew Rate

■ High-Speed Data Storage

■ 60 V Minimum Output Breakdown

■ High Data Input Rate

■ PNP Active Pull-Downs

■ Low Output-Saturation Voltages

■ Low-Power CMOS Logic and Latches

■ Improved Replacements

for TL4810–, UCN5810–, and UCQ5810–

产品属性

- 产品编号:

A6810SA

- 制造商:

Allegro MicroSystems

- 类别:

集成电路(IC) > 配电开关,负载驱动器

- 包装:

卷带(TR)

- 开关类型:

闩锁驱动器

- 输出数:

10

- 比率 - 输入:

1:10

- 输出配置:

高端

- 输出类型:

双极性

- 接口:

并联,串行

- 电压 - 负载:

60V(最大)

- 电压 - 供电 (Vcc/Vdd):

3V ~ 5.5V

- 电流 - 输出(最大值):

40mA

- 输入类型:

非反相

- 工作温度:

-20°C ~ 85°C(TA)

- 安装类型:

通孔

- 供应商器件封装:

18-DIP

- 封装/外壳:

18-DIP(0.300",7.62mm)

- 描述:

IC PWR DRVR BIPOLAR 1

| 供应商 | 型号 | 品牌 | 批号 | 封装 | 库存 | 备注 | 价格 |

|---|---|---|---|---|---|---|---|

ALLEGRO/埃戈罗 |

2021/2022+ |

NA |

6000 |

原厂原装现货订货价格优势终端BOM表可配单提供样品 |

询价 | ||

ALLEGRO(美国埃戈罗) |

23+ |

标准封装 |

6933 |

我们只是原厂的搬运工 |

询价 | ||

ALL |

23+ |

CDIP |

18000 |

询价 | |||

ALLEGRO |

2016+ |

DIP |

6528 |

只做进口原装现货!假一赔十! |

询价 | ||

ALLEGRO |

1315+ |

360000 |

0 |

询价 | |||

ALLEGRO |

23+ |

原厂原包 |

19960 |

只做进口原装 终端工厂免费送样 |

询价 | ||

ALLEGRO |

23+ |

NA |

6000 |

原厂原装现货订货价格优势终端BOM表可配单提供样品 |

询价 | ||

ALL |

2017+ |

DIP-18 |

45896 |

深圳代理原装现货进口库存(香港-日本-台湾)开17点增票 |

询价 | ||

ALLEGRO/雅丽高 |

23+ |

DIP-18 |

90000 |

只做原装 全系列供应 价格优势 可开增票 |

询价 | ||

ALLEGRO |

23+ |

DIP |

3000 |

原装正品假一罚百!可开增票! |

询价 |